Lỗi: Không tìm thấy biểu mẫu liên hệ.

Chương trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

IPC |

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

SPECIALIZED PCBA PRODUCT TECHNIQUES ACCORDING TO INTERNATIONAL STANDARDS

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Chương trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

KỸ THUẬT SẢN XUẤT PCBA CHUYÊN SÂU THEO TIÊU CHUẨN QUỐC TẾ |

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

POWER INTEGRFITY FV & VCLP

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

PHYSICAL VERIFICATION

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

STATIC TIMING ANALYSIS

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

| Program | Subject objectives | Summary of course content |

|---|

| Place & Route Beginner | Knowledge: Electronic circuit design. Details of the physical design stages of electronic circuits.

|

Introducing the role of IC in human life

|

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

CELL DESIGN

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

| Program | Subject objectives | Summary of course content |

|---|

| DFT Intensive Level 1 |

Knowledge:

Skill:

|

Part 1: Overview of the IC test design process including:

Objective: Through this section, students will have basic knowledge about IC test design Part 2: In-depth details about components used to test ICs including:

Objective: Through this section, students will have the following specialized knowledge about IC test design components. Part 3: Introduction to EDA tool used for DFT Insertion section

|

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

DESIGN SYNTHESIGN

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

RTL VERIFICATION

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Programme |

Subject objectives |

Summary of course content |

|---|---|---|

|

RTL DESIGN

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

POWER INTEGRFITY FV & VCLP

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

PHYSICAL VERIFICATION

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

STATIC TIMING ANALYSIS

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

| Chương Trình | Mục tiêu môn học | Tóm tắt nội dung môn học |

|---|

| Place & Route Sơ Cấp | Kiến thức: Thiết kế vi mạch điện tử. Chi tiết các công đoạn thiết kế vật lý vi mạch điện tử.

+ Kỹ năng: Thực hiện thiết kế vật lý vi mạch điện tử ở cấp độ thiết kế block. Bao gồm các kỹ năng: Import, Floorplan, Placement, Clock Tree CTS, Routing. + Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

Giới thiệu vai trò của IC trong cuộc sống của con người

– Ôn tập lại các kiến thức cơ bản về kỹ thuật số và kỹ thuật điện – Giới thiệu sơ lược quy trình để tạo ra 1 IC – Trình bày quá trình thiết kế 1 block từ khi nhận dữ liệu đầu vào đến khi kết thúc thiết kế. |

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

CELL DESIGN

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

| Chương Trình | Mục tiêu môn học | Tóm tắt nội dung môn học |

|---|

| DFT Chuyên sâu cấp độ 1 |

Kiến thức:

Kỹ năng:

|

Phần 1: Giới thiệu tổng quan quá trình thiết kế kiểm tra vi mạch bao gồm:

Phần 2: Chi tiết chuyên sâu về các thành phần dùng để kiểm tra vi mạch bao gồm:

Mục tiêu: Thông qua phần này sẽ giúp cho học viên có các được kiến thức chuyên sau về các thành phần thiết kế kiểm tra vi mạch Phần 3: Giới thiệu về EDA tool sử dụng cho DFT phần Insertion

|

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

IPC

|

Kiến thức: Tiêu chuẩn chấp nhận các sản phẩm lắp ráp điện tử |

– Sinh viên tốt nghiệp Đại học, Cao đẳng, Trung cấp… – Nhân viên, Quản lý tại các công ty điện tử:

|

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

DESIGN SYNTHESIGN

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

RTL VERIFICATION

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

Chương Trình |

Mục tiêu môn học |

Tóm tắt nội dung môn học |

|---|---|---|

|

RTL DESIGN

|

Lắp ráp mạch điện tử trên dây chuyền sản xuất công nghiệp. o Thành thạo kỹ thuật Through holes. Nắm vững, vận dụng tốt các quy chuẩn quốc tế trong ngành sản xuất PCBA. -Thái độ, chuyên cần: Tham gia lớp đầy đủ và chuẩn bị cho giờ lên lớp theo yêu cầu của giáo viên. |

– Giới thiệu vai trò của PCBA trong cuộc sống của con người – Nhận dạng, kiểm tra linh kiện và các nguyên vật liệu sản xuất. – Quy trình sản xuất PCBA và các tiêu chuẩn kỹ thuật quốc tế. – Kỹ thuật Though holes – Kỹ thuật SMT (Surface Mount Technology) – Xử lý sự cố kỹ thuật trong quá trình sản xuất |

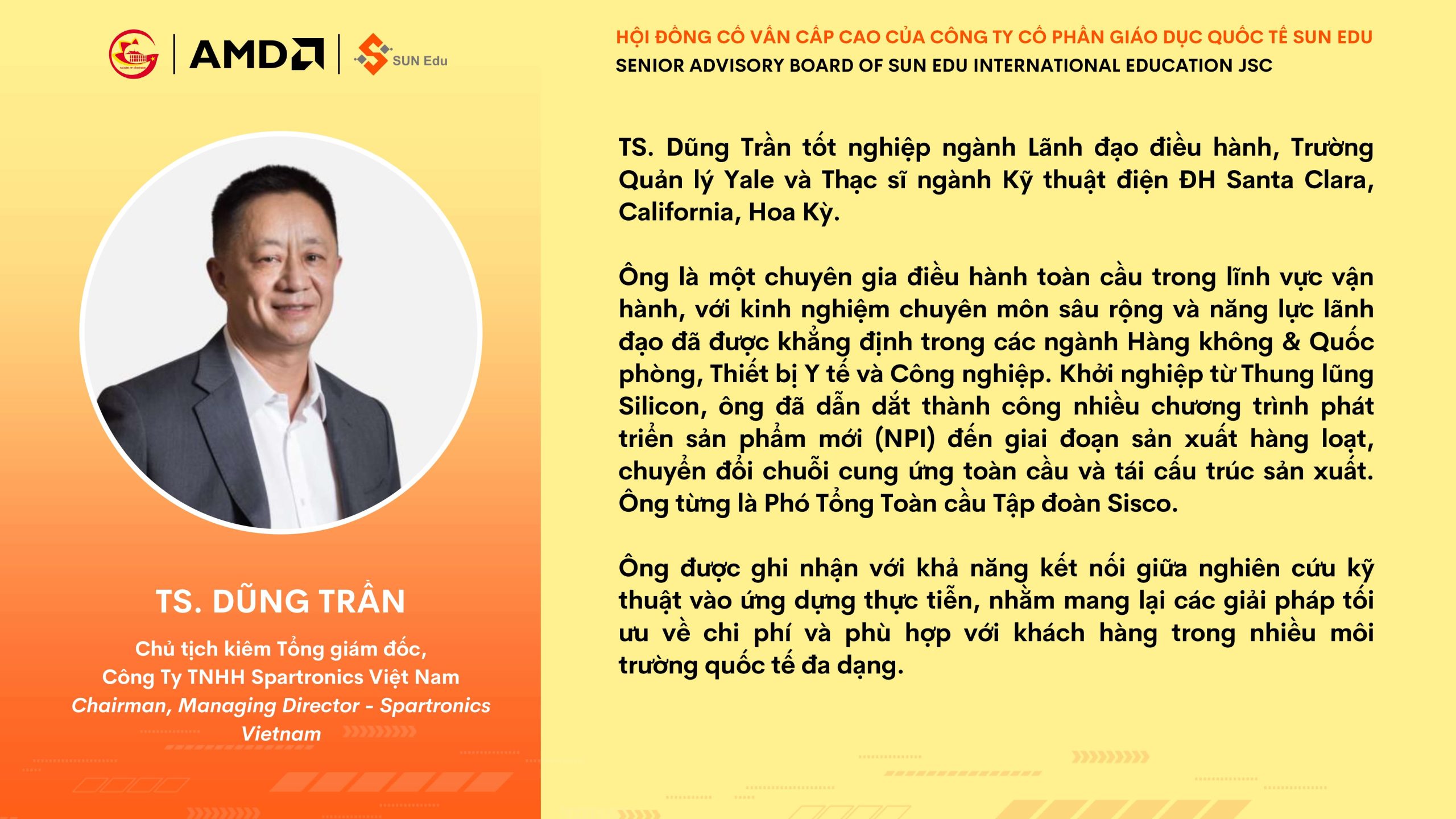

Position:

Specialize:

Education:

Career:

Honors and Awards:

Analog Inference, Inc., Santa Clara, CA

July 2021– Present

Crossbar, Inc., Santa Clara, CA

Nov 2014 – July 2021

Crocus Technology, Inc., Santa Clara, CA

Jan 2013 – Nov 2014

SanDisk Corp., Milpitas, CA

Jan 2012 – Dec 2012

AAE Systems Inc., Sunnyvale, CA

Dec 2002 – Nov 2011

ComTier Inc., Sunnyvale, CA

Apr 2001 – Sept 2002

Advanced Micro Devices, Sunnyvale, CA

Jun 1999 – Apr 2001

Bachelor of Science in Electrical Engineering – 1998

Minor in Computer Science

Sacramento State University

Synopsys Education and Training Services:

REFERENCES: Available upon request.

STATUS: US citizen

Language: English, Vietnam

Degree: Ph.D. in Electronics Engineering, Gunma Universit

Title: Vice President & Chief Technology Officer of Innovative Solutions (INOSO)

Specialized: Develop super Low Power Consuming microchips. Design Process Flow for Semiconductor Fabrication (Fab), Develop the workforce for High Yield Fab through engineers and students training.

Experience:

Bonus prize:

Patents:

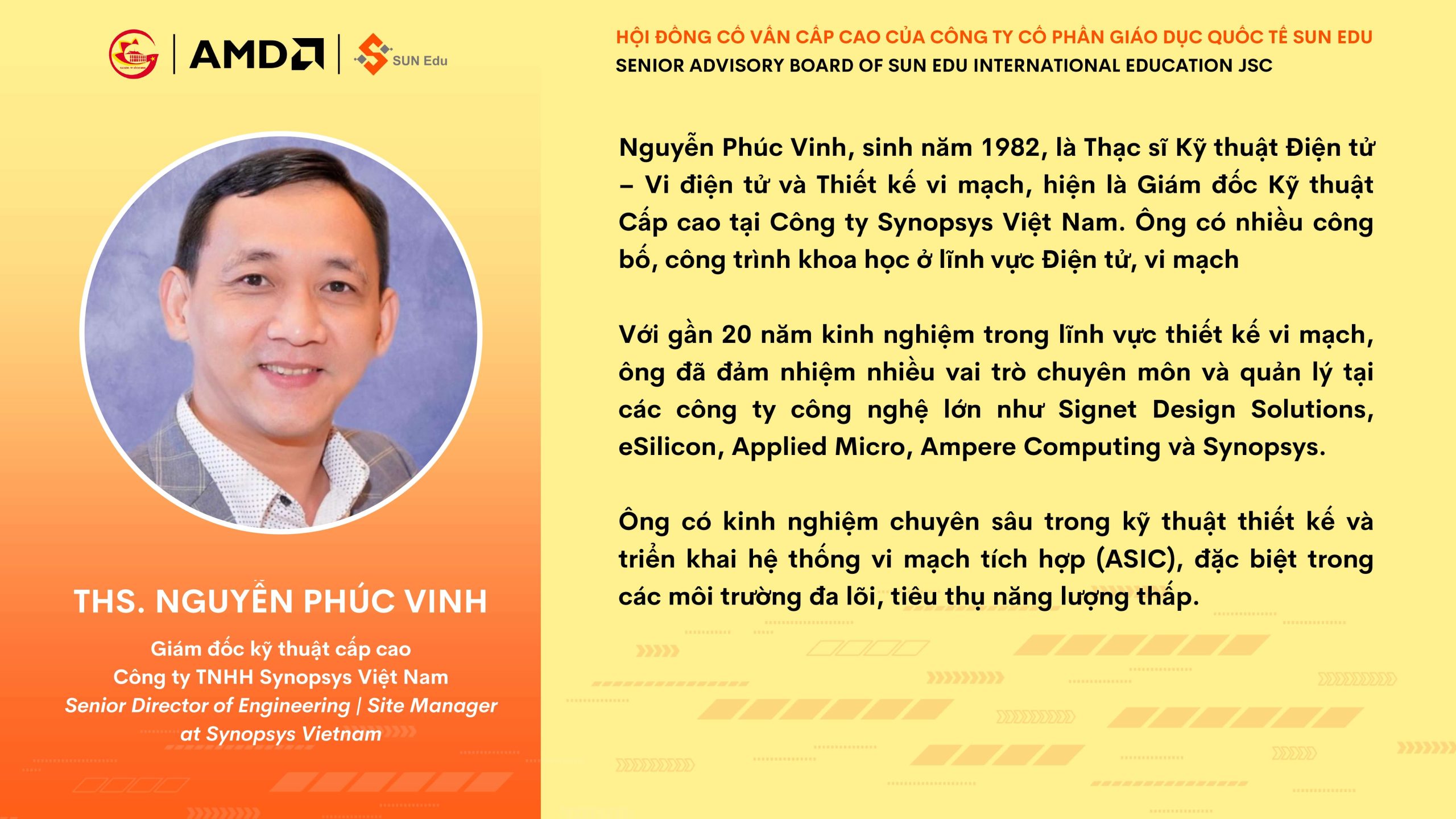

Position: Senior Advisor

Education:

Lab Skills:

Previous Employment:

Education:

Career and Titles:

Position: Board Advisor

Education:

International Experience:

Industry Sector Experience:

Previous Employments:

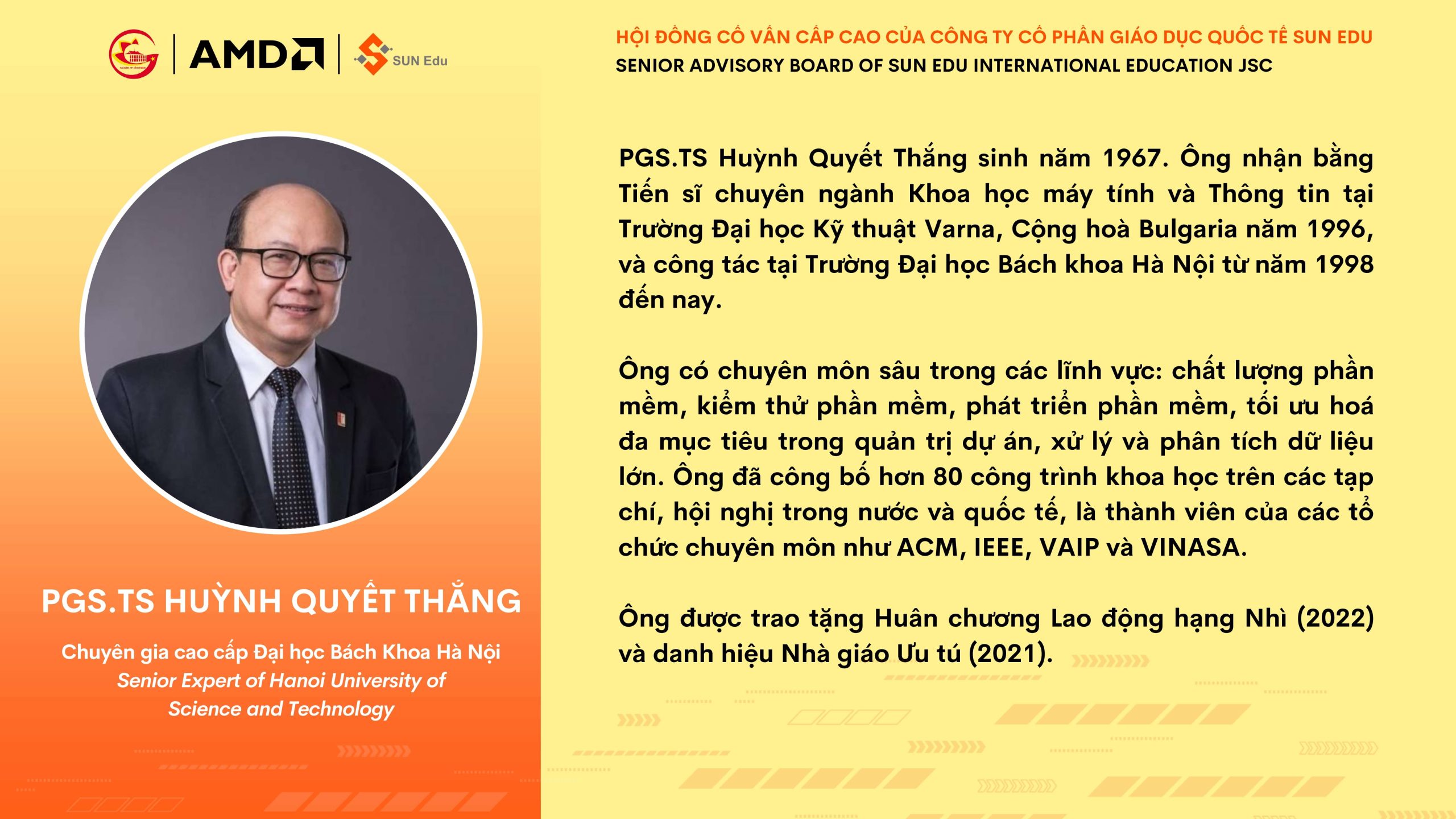

Title & Affiliation:

Education:

Expertise:

Recent Projects:

Awards:

Education and Positions:

International Achievements and Experience:

Title & Degree

Published Works:

Positions:

Awards:

Học vị: Tiến sĩ chuyên ngành Kỹ thuật Điện tử, Đại học Gunma

Chức danh: Phó Chủ tịch kiêm Giám đốc Công nghệ Giải pháp Sáng tạo (INOSO)

Chuyên ngành: Phát triển vi mạch siêu tiêu thụ điện năng thấp. Thiết kế quy trình chế tạo chất bán dẫn (Fab), Phát triển lực lượng lao động cho Fab năng suất cao thông qua đào tạo kỹ sư và sinh viên.

Kinh nghiệm:

Khen thưởng:

Bằng phát minh:

Chức danh & Bằng cấp:

Tác phẩm đã xuất bản:

Chức vụ:

Giải thưởng:

Chức vụ: Cố vấn cấp cao

Giáo dục:

Kỹ năng thí nghiệm:

Chức vụ đã đảm nhận: